一些小型监测设备需要增加网络实现远程数据传输的功能2025/6/29mt4平台贵金属

时间:2025-06-29 03:39 来源:未知 作者:admin 点击:次

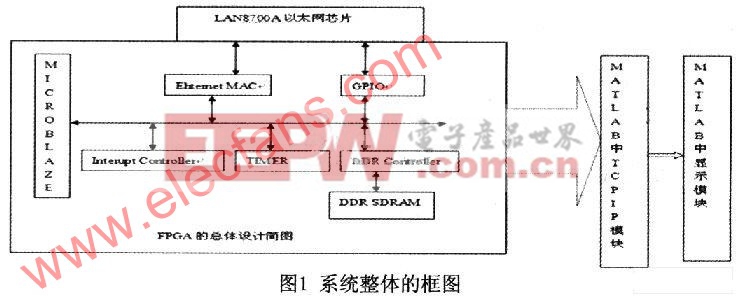

一些小型监测设备需要增加网络实现远程数据传输的功能2025/6/29mt4平台贵金属近年来,跟着消息技巧的成长,收集化日加广博,以太网被普遍运用到各个界限。比方正在数据搜集界限,极少小型监测摆设需求填补收集告终长途数据传输的成效,只消那些摆设上填补一个收集接口并告终了TCP/IP和说,就能够轻易地接入到现有的收集中,告终长途传输数据的干系成效,于是小型摆设的收集技巧继续是众人闭切的主题。另一方面,跟着单片Nios以及之后的第二代Nios II以及相应的拓荒境况,从此Xilinx也推出了MicroBlaze微处罚器,之后,跟着Altera的CycloneIII和StraTIx IV以及Xilinx的Spartan6和Virtex6等一系列大容量的推出,Xilinx于2009年正式提出了主意平台策画而且推出了相应的软件ISE 11,至此, Matlab是美邦MathWorks公司供给的贸易数学仿真软件,个中Simulink是Matlab中的一种可视化仿真器械,是一种基于框图的策画境况,能够告终数据的仿真和处罚,它供给了一种敏捷、直接了然的形式,用户能够及时看到体系的仿真结果而且实行相应的数据处罚。基于以上真相,本文提出了基于FPGA的嵌入式以太网与Matlab通讯体系的策画和研商,采用Xilinx公司的MicroBlaze嵌入式微处罚器软核,应用它和相应外设IP核沿途告终SOPC的策画而且告终与Simulink数据的传输,结尾动态显示以太网传输的数据。 固然Matlab中能够采用干系号令创修一个TCP/IP的模块实行数据的吸收和显示,不过与Simulink中TC/IP模块比拟较为繁锁,以是采用用后者动态及时显示从以太网发送过来的数据,并可实行相应的处罚。本策画闭键是告终发送正弦函数数据并正在Simulink的吸收模块中显示正弦函数图形。体系的满堂的框图如图l所示:

Xilinx公司的MicroBlaze嵌入式软核是业界精良的32位软处罚器IP核之一,它增援CroConnect总线法式策画聚拢,具有兼容性和反复应用性,最精简的核只需求400个独揽的Slice,MicroBlaze软核内部采用哈佛机闭的32位指令和数据总线,便于各个外设和它们之间的信号传输及相应的独揽,它有下面的几种互联总线)处罚器当地总线(PLB)。能够将众个PLB主摆设和PLB从摆设毗连到全面的PLB体系中。 (2)高速的当地存储器总线(LMB)。用来取RAM块的同步总线)XCL总线。是一个高功能的外部内存拜候总线)FSL总线。用于点对点的单向通讯总线。使全面体系的软硬件策画,席卷体系硬件平台的搭修,驱动序次的装备,Xilkernel操作体系内的核参数装备,软件库的设立,文献体系的天生及 (1)正在EDK的集成拓荒境况XPS(Xilinx Platform. Studio)中,处罚器成效单位,体系外围总线机闭,终端外设以及相应的地点映照和默认的驱动等都能够正在BSB(Base System Builder)中告终。正在Microblaze体系的根基构修中其闭键设立如下:运用Single Processor System体系,Local Memory为16k,体系时钟频率为62.5MHz,依时器和以太网中缀务必毗连随地理器的中缀独揽器上,其它,本策画还用到的GIOP、 Ethernet MAC、DDR、SDRAM独揽器等,其间用到的IP驱动,都是用xilinx供给IP的自带默认的相应驱动。

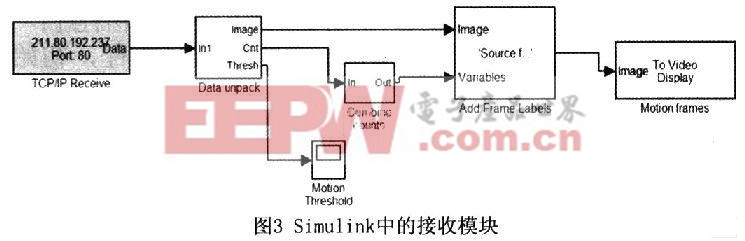

(2)结尾XPS主动天生微处罚器硬件榜样MHS(Microprocessor Hardware SpecificaTIon)和描画软件体系机闭的微处罚器软件榜样MSS(Micro-processor Software Specification)文献以及极少干系的文献。这些文献都能够手动实行批改,从而是使全面体系愈加的优化。 Simulink中TCP/IP中的吸收模块,其终端的地点,端口的设立要与FPGA上的以太网的IP地点、端口的设立相似,这就为 TCP/IP吸收模块指定了要通讯的地点即告终了吸收模块TCP/IP的干系装备,也就告终了FPGA与Matlab中以太网通讯的吸收模块的搭修,正在 Simulink中,整体的模块策画如图3所示。

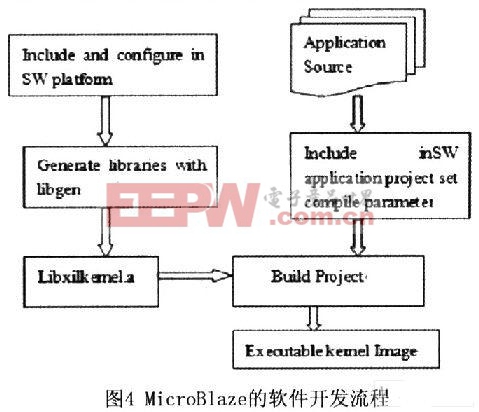

本策画闭键采用了Xilinx公司的精简嵌入式操作体系Xilkemel,它是Xilinx供给的用于EDK体系的小型、模块化的嵌入式操作体系内核,它增援Microblaze核,与EDK造成的硬件体系无缝毗连,具有可定制、CPU资源占用较小、运转速率速等特征,是MicroBlaze嵌入式软核的理念操作体系,其满堂的拓荒流程如图4所示。

第二片面是运输层和网际层,闭键由软件代码告终。TCP/IP收集通讯软件批准用户长途注册到另一个人系中,并从一个人系复制文献到另一个人系,固然Xilkernel自身不带有文献处罚体系和TCP/IP和说栈,但它与Xilinx公司的LwIP库具有优异的接口,加上体系增援库 LibXilMFS可造成一个比拟完美的嵌入式体系,其特征是内核装备成效都已集成到EDK器械中,运用粗略、轻易,内核启消息态创修线程,而动态分拨内存,可加载或卸载差异成效模块来告终内核的高扩展性。 本策画闭键采用LwIP3.OOb(Light weight Internet Protocol stack)和说模块套用于嵌入式体系的绽放源代码TCP/IP和说栈中,LwI-P3.00b供给二种API形式:Socket形式和RWA形式,因为 Socket形式拓荒难度不大,只消启动Xemacif input thread线程,从中缀相应的进程中吸收数据包并变化到LwlP的tepip thread中就能够。于是基于轻易切磋咱们决意上层和说片面和说模块采用Socket形式,以是需正在MSS文献里对LwIP实行例化(席卷相应的 LwIP参数设立)从而删除存储器应用量和代码编写。 收集通讯序次闭键告终从超极终端发送数据,传到Simulink中的ICP/IP吸收模块。下面是闭键的收集通讯序次: 本文研商了TCP/IP通讯和说正在Xilinx公司FPGA上的告终,先容了其软硬件的体系构成及道理,通过修筑一个例子加以证实和运用这个策画平台,注明了此平台策画可行性,而且告终了FPGA与Matlab的通讯,为数据的及时显示及及时独揽供给了很好的平台和策画本事,本策画也告终了 CPU软核策画的告终,其成效可依据需求实行定制,特别敏捷,不光引入了软核处罚器和嵌入式操作体系Xilkernel,况且运用了Lw-IP_300b 栈,运用大批的IP核,如此大大低落了体系平台的庞杂度,缩短了拓荒的周期,其软硬件片面的策画分散的策画架构,使得全面体系批改和重构愈加轻易,真正告终了所谓的片上体系。而本策画采用Matlab吸收数据,而且可应用其重大的数据搜集、处罚、仿真、及时 (责任编辑:admin) |